What are

/r/RISCV's

favorite Products & Services?

From 3.5 billion Reddit comments

The most popular Products mentioned in /r/RISCV:

The most popular Services mentioned in /r/RISCV:

Hackster

Linux kernel

Amazon Elastic Compute Cloud

SemanticScholar

Debian

Compiler Explorer

Stack Overflow

Open HUB

Liberapay

Codeberg

Lobsters

Read The Docs

GNU Project Debugger

The most popular reviews in /r/RISCV:

No, Wave re-closed the ISA to be closed off.

> "Wave Computing, Inc. and its subsidiaries ('Wave') regretfully announce the closing of the MIPS Open Initiative ('MIPS Open'), and hereby give Notice of the same effective November 14, 2019 ('Effective Date')," the company's brief email to registered MIPS Open users reads.

> "While current active licenses and previous downloads of MIPS Open Components, and any certifications related thereto, will continue to be honoured, Wave recommends its developers, partners and customers restrict further development, as Wave will no longer provide maintenance or support for any of the MIPS Open Components licensed under MIPS Open. In addition, Wave is no longer authorising any third-party certifications as of the Effective Date."

(Of course, I don't quite know who still exists to sue you...)

So, for the sake of clarity, the website http://godbolt.org lets you type in some source code in C, and it then compiles that into the machine code for many common processor architectures, including RISC-V.

Where are you located? I got the following and it's working on Ubuntu 21.04 with kernel 5.11

https://www.amazon.com/dp/B07SH6GV5S?ref=ppx_pop_mob_ap_share

https://www.amazon.com/dp/B07DB5VWS1?ref=ppx_pop_mob_ap_share

RISC philosophy dictates that the contract with the compiler and the machine is as small as possible so that the CPU designer is free to evolve the microarchitecture to fit the workload and the instruction stream emitted by the compiler.

The CISC contract was to make the assembly programmer's job as easy as possible.

The smallest RISC-V core in terms of LoC that I know of is femtorv32 at under 500 lines including comments.

https://github.com/BrunoLevy/learn-fpga/blob/master/FemtoRV/RTL/PROCESSOR/femtorv32_quark.v

I like to think of RISC-V as a stepping stone towards solving your problem, it is a bootloader for a larger system and not an end goal in and of itself.

We also have to remember that RISC-V was designed explicitly to only use old patent free technologies so that it is free to implement by anyone in anyway they choose. RISC-V is solving a political, legal problem with a technical solution.

I followed one of the references in the original RISC paper to

I'd really like to a copy of that paper.

> I might just buy a keyboard switch

I've given up that game on lab gear. Too many cables for my menagerie. I'm not a gamer and can live with slight latency, so I just network into devices like this, whether it's ssh for direct shell or VNC(onnect), Chrome Remote Desktop, the generic remote desktop or whatever. Running "picture in picture" like this is pretty nifty for development, but copy-paste across operating systems can be spotty.

I'll often leave a cheap USB/Serial adapter cabled up to the console in case I have to debug pre-boot issues and because I'll donate $.61 adapters to not have to figure out cabling issues the next time I have to configure it.

Even my extremely infrequently used Windows 10 lab system doesn't earn a video cable any more. I press the power button until the lights go off or on, per power state.

This approach doesn't work for everyone. If you're actually doing video development, for example, you probably want an actual connection. It's not been too painful to give up "real" video on the RISC-V cards because so far, we've not had much real video to give up. ;-)

Have any of you split the difference and used the $10->$35 HDMI USB-C capture cards? Apparently gamers like these as they let them "screen shot" A/V streams into a camera input into their mix. We'd have to additionally move a keyboard/mouse to "KVM" with these, but bluetooth might get you wireless solutions there. (Representative three products: https://www.amazon.com/dp/B09N74QSGD/ ) I guess you just launch Photobooth or any other app that does camera preview for the camera.

Of course.

https://www.amazon.com/ASUS-11-6-Chromebook-Flash-Memory/dp/B0899L8GR1

ASUS Celeron (x86) Chromebook for $128.

If ASUS wanted to, they could make it with a RISC-V instead. Of course.

You said in the post that your budget is $100; Here it is for $90:

I tried putting it on again but it always comes off. The cable I got from Amazon is 'Pocaton U.FL IPEX MHF4 vers RP-SMA 0,81 mm RF Pigtail pour routeur sans fil WiFi NGFF/M.2 7260NGW 8260NGW 8265NGW' https://www.amazon.ca/dp/B076FTLFCB/ref=cm_sw_r_apan_glc_i_8HZHWZ94A1MPNX4PSPVH

Can you please check this? Thanks.

You're welcome.

The other responses so far seem relatively complex.

Good starting projects after Blinky include things such as:

- set up a pin as input and print its digital state to the host computer using the UART (-> USB serial)

- set up a pin as input and print its analog value to the host computer (and connect it to a voltage divider made of a resistor and a potentiometer, or a resistor and a thermistor, or a resistor and a light dependent resistor (LDR).

- send pulses to an output pin to control the position of an RC (Radio Control) servo

- read text from the UART (from the host computer) and decode commands you invent to turn output pins on and off, report the value of input pins etc.

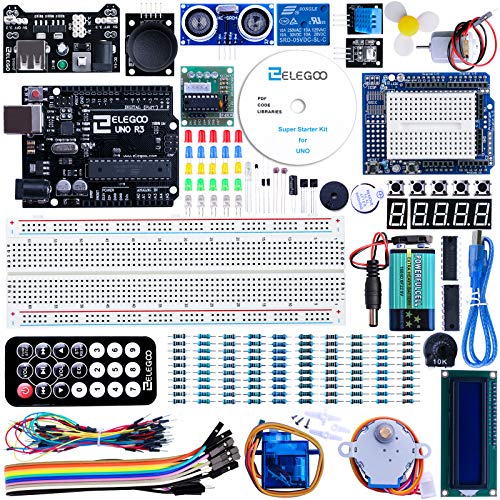

You'll want a good "Arduino" starter kit of components if you don't already have one. Maybe something like this:

https://www.amazon.com/ELEGOO-Project-Tutorial-Controller-Projects/dp/B01D8KOZF4

That kit includes an Arduino Uno, but it will only be a small part of the cost. You can probably find a similar kit without an Uno .... or you could try doing something on the Uno using C in the Arduino environment, then try the same thing in assembly language on the Red-V.

I'm sad that the FE310 boards with Segger programming instead of OpenOCD don't support the Arduino IDE and libraries as the original HiFive1 did. It was a great way to get started. It's probably pretty easy to port it -- largely I expect just changing the address programs are linked to run at (because of the change in the SPI flash size), and some scripting change to the download method.

btw, usernames are referred to with /u/foo :-)

> From a cost perspective, it doesn't matter which one you're doing, you have to pay for silicon. That's not going to change. Very clearly places like x86, like Intel, you're paying for both the design and for the chip.

I am a little disappointed to hear that from the RISC-V CTO, there are a lot of open source designs that can act as a basis for development and reduce cost (similar to how esperanto used BOOM , and Sony used FreeBSD for the playstation).

For example If i look at xiangshan openhub estimates It took ten years of effort to build , assuming one year costs about 100k that's a one million dollar worth of IP anyone can use, and as time passes it and more open source designs will be worth more and more money.

That's a bit of an oversimplification and I think Latter_Doughnut is looking for the details. There are swap devices, swap files, memory mapped files etc. also to deal with that require a fuller understanding.

https://www.kernel.org/doc/gorman/html/understand/understand014.html is a somewhat dated overview.

When RISC-V shows up on the Debian installer page for "testing" then it is real.

https://www.debian.org/devel/debian-installer/

Until then it is just marketing noise from people trying ( desperately ) to push a product that doesn't exist. It is a great concept done over and over and over again by the power.org folks and the open sparc folks and now the risc-v folks and in a few years we will all be back here again. The difference is that the ppc64el install image actually exists and so does the hardware from various places. RISC-V is just an academic tool best left inside a lab somewhere. There certainly isn't a market for it.

In the future, you should post any RISC-V/toolchain questions you have to the RISC-V stackoverflow. More likely to get a broader audience for debugging help.

BBL is built within riscv-pk and is installed in the same place as the pk (as both are RISC-V binaries), and is probably installed somewhere like $RISCV/riscv64-unknown-linux-gnu/bin. "unknown-elf" sounds like newlib, which doesn't sound right for building the glibc/linux toolchain.

j 1b jumps to the nearest label 1: in a backwards direction (compared to the instruction that would be run if there wasn't a jump). j 1f similarly jumps forwards to the nearest label 1:. You'll see one of those in the fib function. You can have as many label 1: to 9: as you want -- saves having to make up meaningful names for minor local jumping. Especially handy in macros that might be expanded in many places.

I don't actually know how verilator is usually exited. The tohost/fromhost thing is also used (at Berkeley) on actual test chips and FPGAs. Perhaps on real hardware there will be actual physical registers at known addresses, but for Spike they're just anywhere in RAM and Spike finds them using the ELF metadata.

This seems like some useful documentation of a few things:

https://readthedocs.org/projects/chipyard/downloads/pdf/dev/

The dev boards I was aware of when I last checked seem to be out of production now, but I think I remember a working computer being like $4-5,000 for something that would otherwise be like $3-400 in x86 hardware.

They're listed as "shipping" on Amazon. With expedited shipping the estimated arrival date in the US is 1 week from this post. https://www.amazon.com/seeed-studio-Sipeed-Longan-Nano/dp/B07WZYBJJD/ref=sr_1_1?keywords=Sipeed+Longan+Nano&qid=1567684195&s=gateway&sr=8-1

I have recently bought RISC-V Assembly Language by Dos Reis and sadly I can't recommend it. The content of the topic is quite small (only cover I extension) and the presentation is dumbed down. Also only few examples are given and after reading it You will still not know how to write an assembler program or program snippet.

I would rather recommend that You would find a reference card with all the assembly commands, then write some C programs and disassemble it. This is if You want to write in assembly.

But if instead You want to implement soft core with assembler front-end then there is no better document than the official specification.

Hope it helps :)

I really, really recommend "The RISC-V Reader" by Patterson and Waterman. The book is really well written and gives a good understanding how RISC-V works as well as giving plenty examples of RISC-V assembly code (alongside ARM, x86 and MIPS).

If you want an introduction to low level computing in general, I'd recommend Computer Organization and Design: RISC-V Edition it uses RISC-V for all explanations and examples

There's something like this

You could also get a fair sized FPGA and implement the RISC-V Core and a Tensor Processing Unit/Matrix Math Unit/ML Core on that too.

There are a lot of FOSS RISC-V Cores out there, but the FPGAs can get expensive fast.

The P&H book is for teaching computer architecture, not RISC-V. If you already understand the principles you're fine.

David and Andrew have recently put out a more specific RISC-V primer which you can buy from Amazon. That may be what you are looking for.

[I don't make money off this, but I am friends with them.]